当前位置:首页>> 全加器的逻辑图

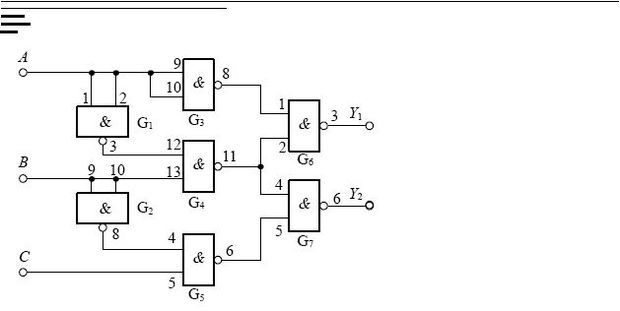

全加器逻辑电路图

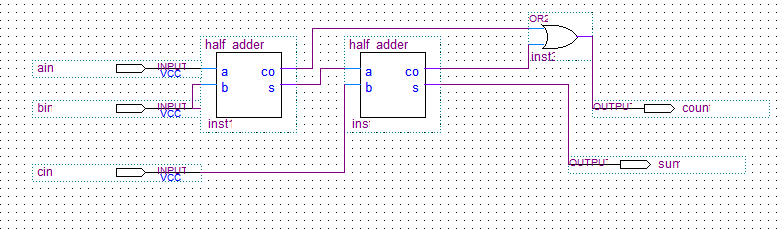

华理数字逻辑实验二全加器

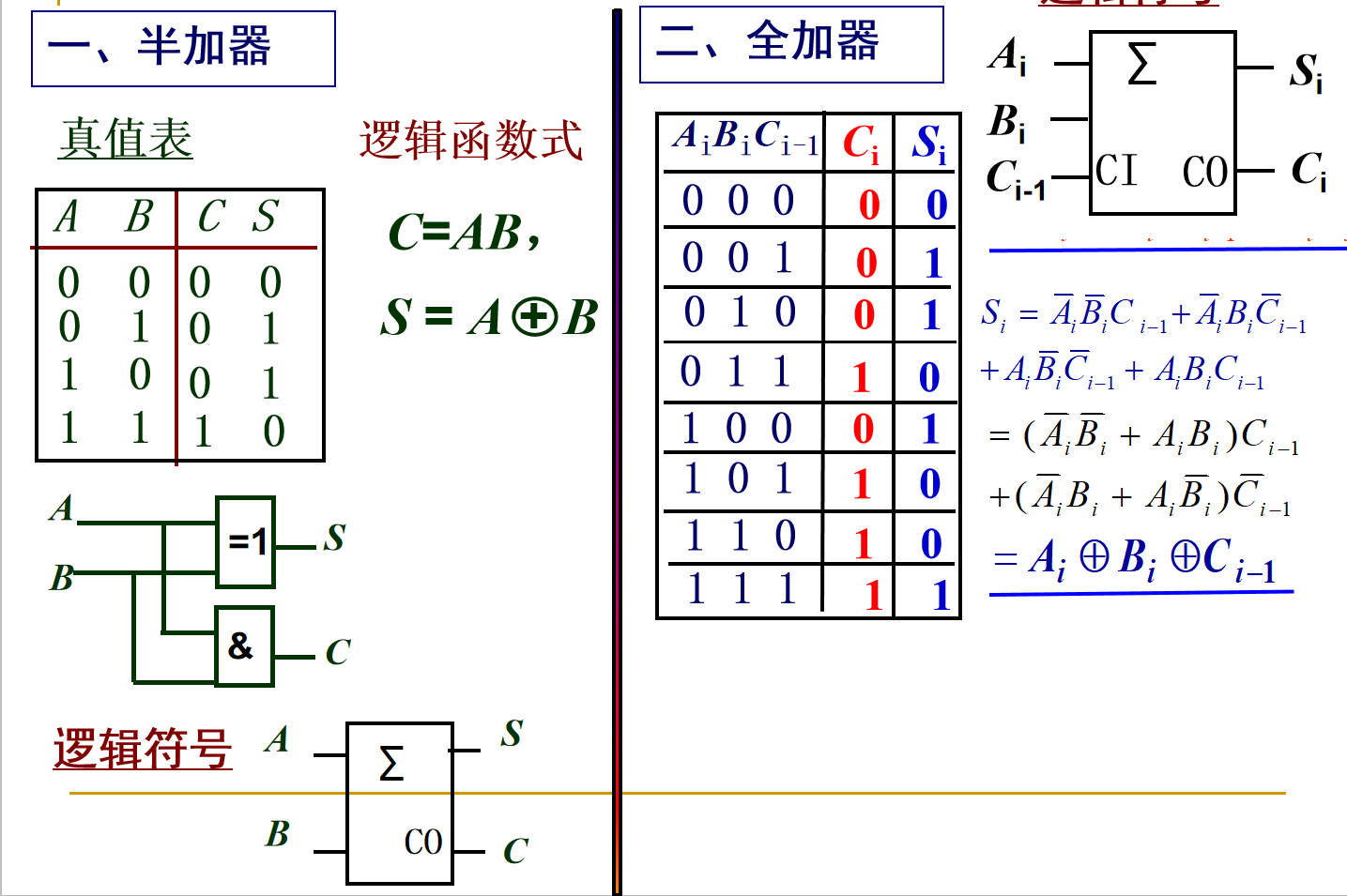

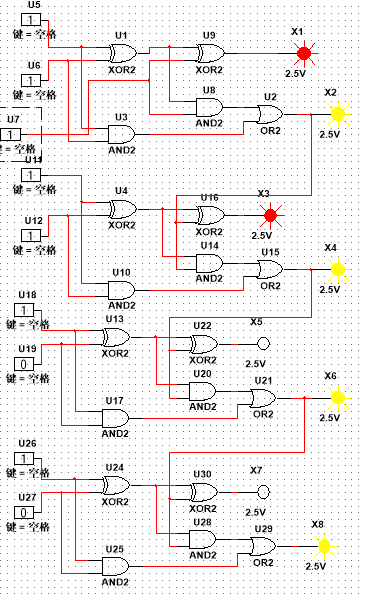

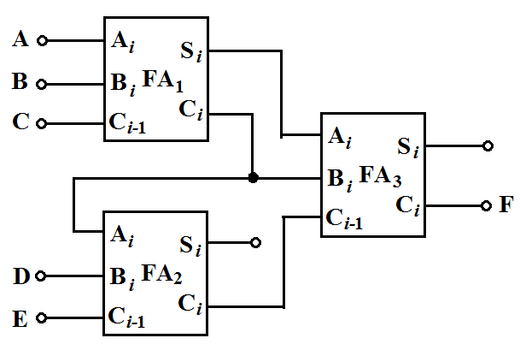

电子/电路 一位全加器实验电路方法的研究 4 种门电路来实现,逻辑电路

全加器逻辑电路图

实用一位加法电路

从零开始构建现代计算机–第二章,01

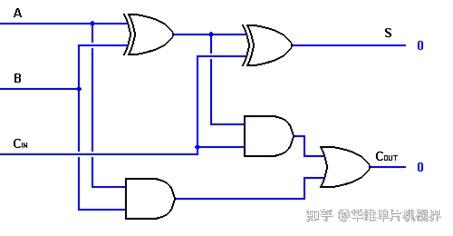

设计一个数字逻辑中的全加器,要求有实验原理,函数表达式,卡诺图,逻辑

全加器

课题名称组合逻辑全加器

全加器电路

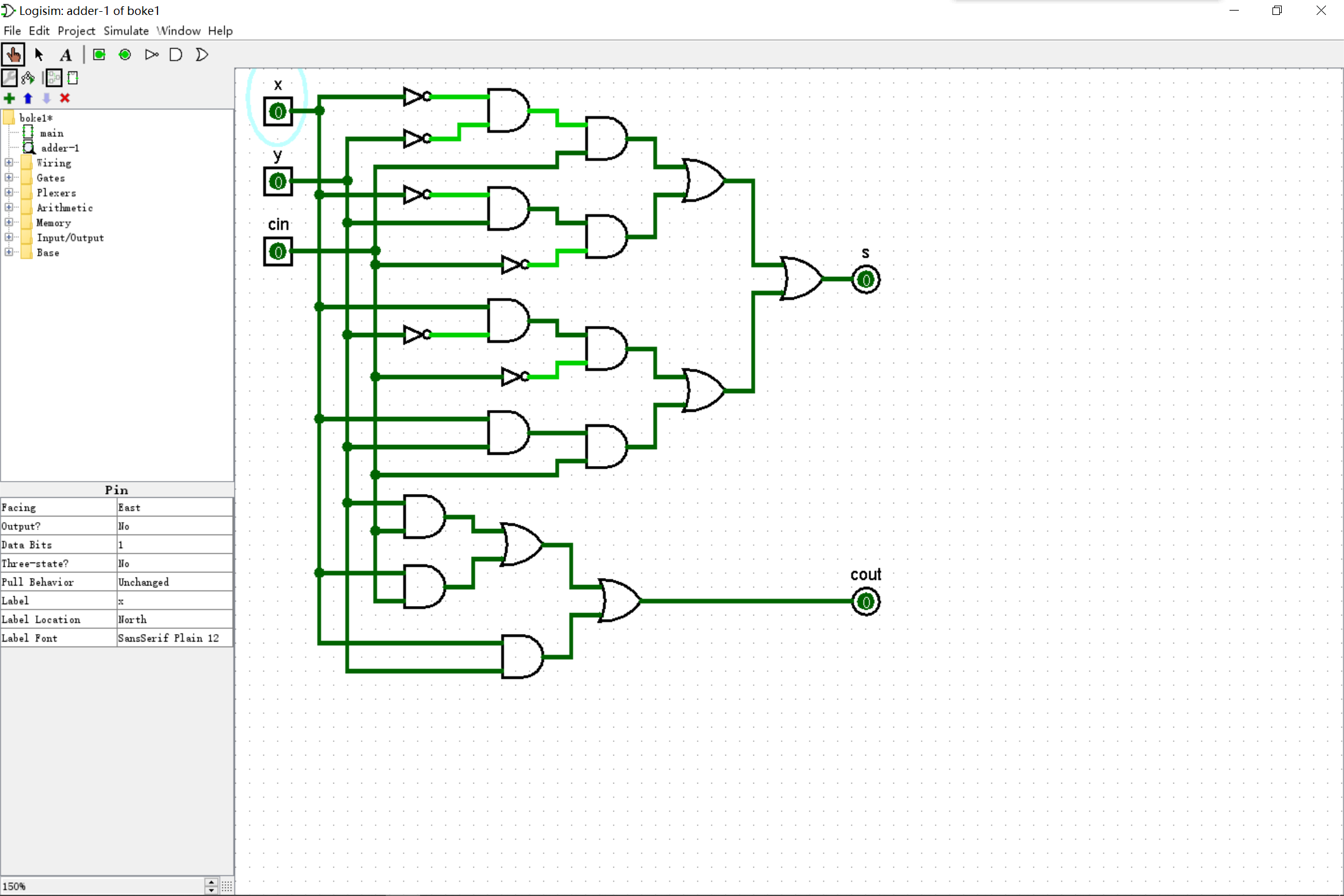

logisim之4位全加器实现以及七段数码管显示

采用逻辑处理方法实现加法运算的数字电路

用4:1数据选择器实现全加器逻辑功能

一位全加器

eda技术讲义 eda技术讲义 全 加 器 被加数,加数以及低位的进位三者

一位二进制全加器

从零开始搭建一个8位计算机系列(二):搭建4位全加器

然后再将x,y和进位数通过全加器进行全加,就是alu的逻辑结构结构

二进制全加器只涉及一位加法逻辑图和电路图

1位全加器有()个输入端,()个输出端

如何只用与非门实现全加器,求逻辑图

单片机入门数字电路基础之什么是半加器,什么是全加器

数字电路与逻辑设计:用74138实现一位全加器!

全加器电路,包括:数据输入电路模块,数据输入电路模块包括逻辑与门和

逻辑电路图 ③使用全加器元件,设计8位串行进位加法器电路

据此可以画出1位全加器的逻辑图:为了比较方便地获得与

从0到1构建计算机(3/12)

quartus ii 之1位全加器

基于多数决定逻辑非门的低功耗全加器设计

一位全加器的多种实现方法1ppt

更多相关内容:

© 微语生活图库,此页面图片不可商用

微语生活图片下载 使建于2016年,当前更时间:2024-09-25 15:00:47

全加器的逻辑图图片下载