当前位置:首页>> 8位全减器逻辑图

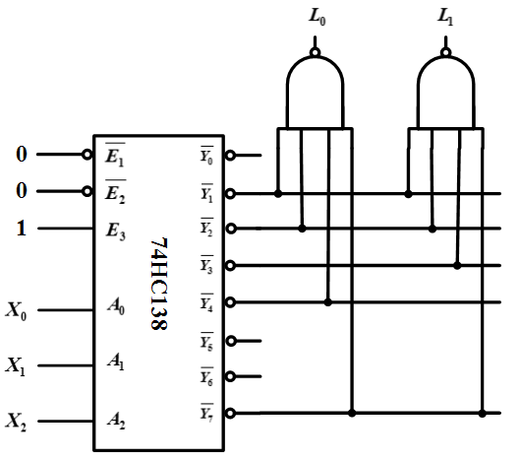

这是38译码器设计的1位二进制全减器,输入为被减数,减数,和来自低位的

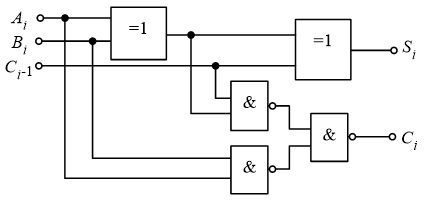

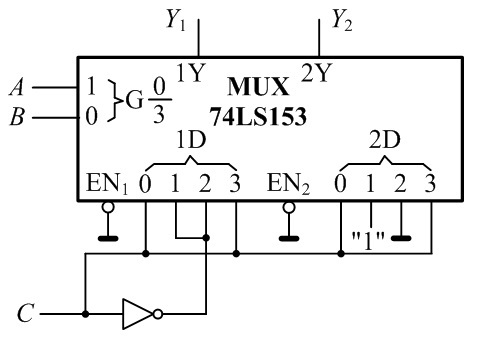

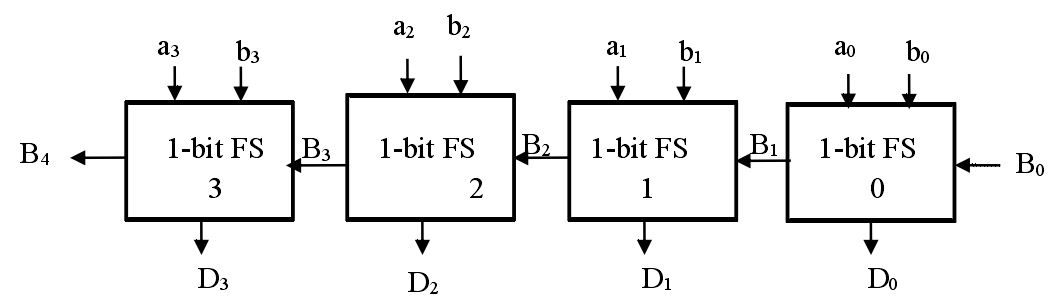

仿照全加器画出1位二进制数的全减器:输入被减数为a,减数为b,低位来的

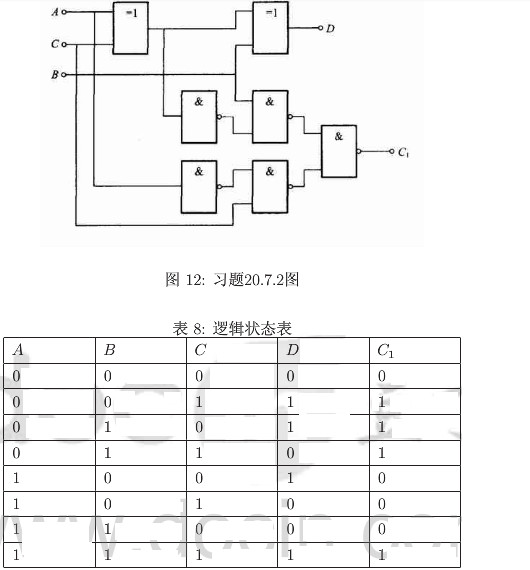

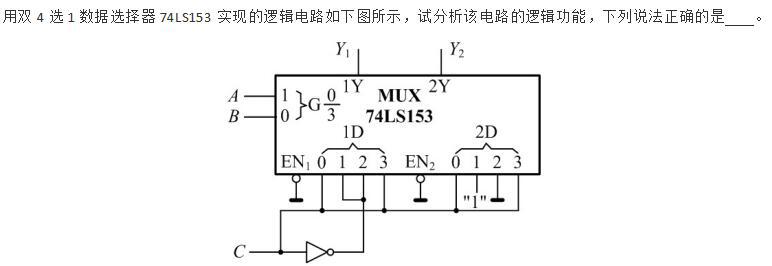

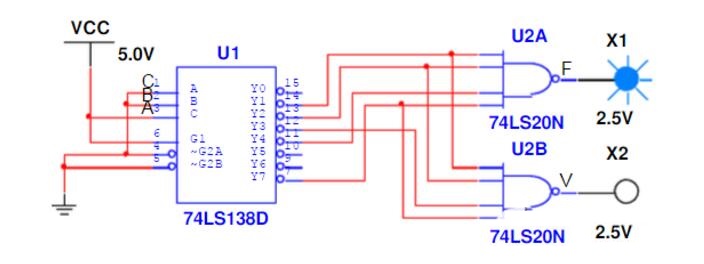

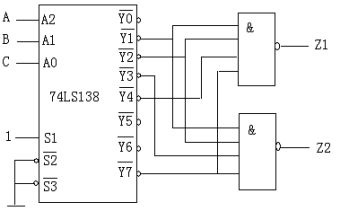

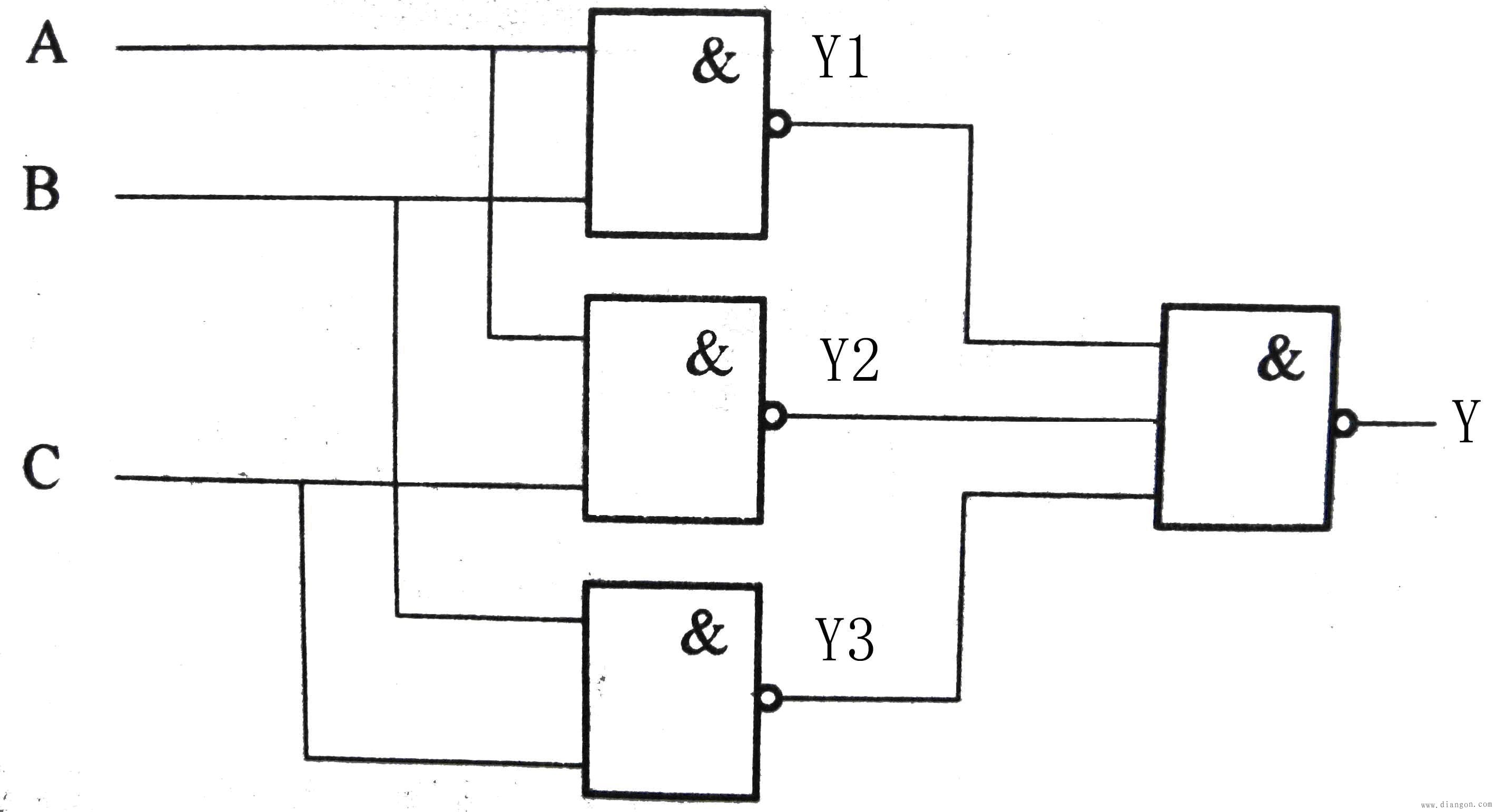

[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为

全减器

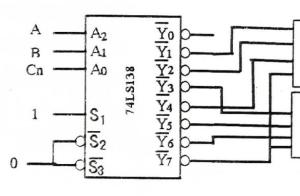

74ls138三线—八线译码器实现,逻辑图如下: 全减器

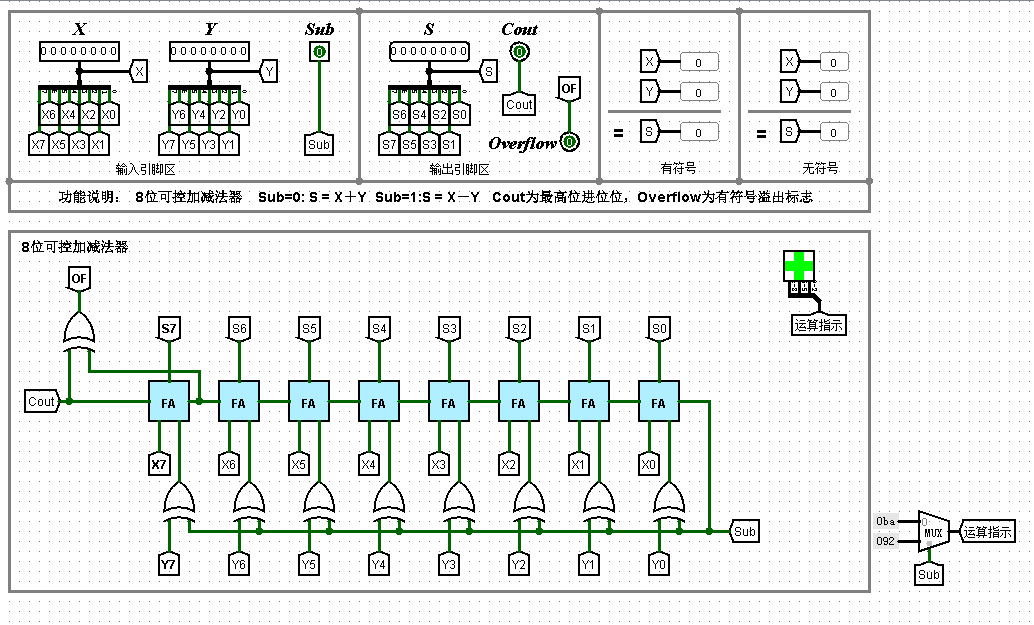

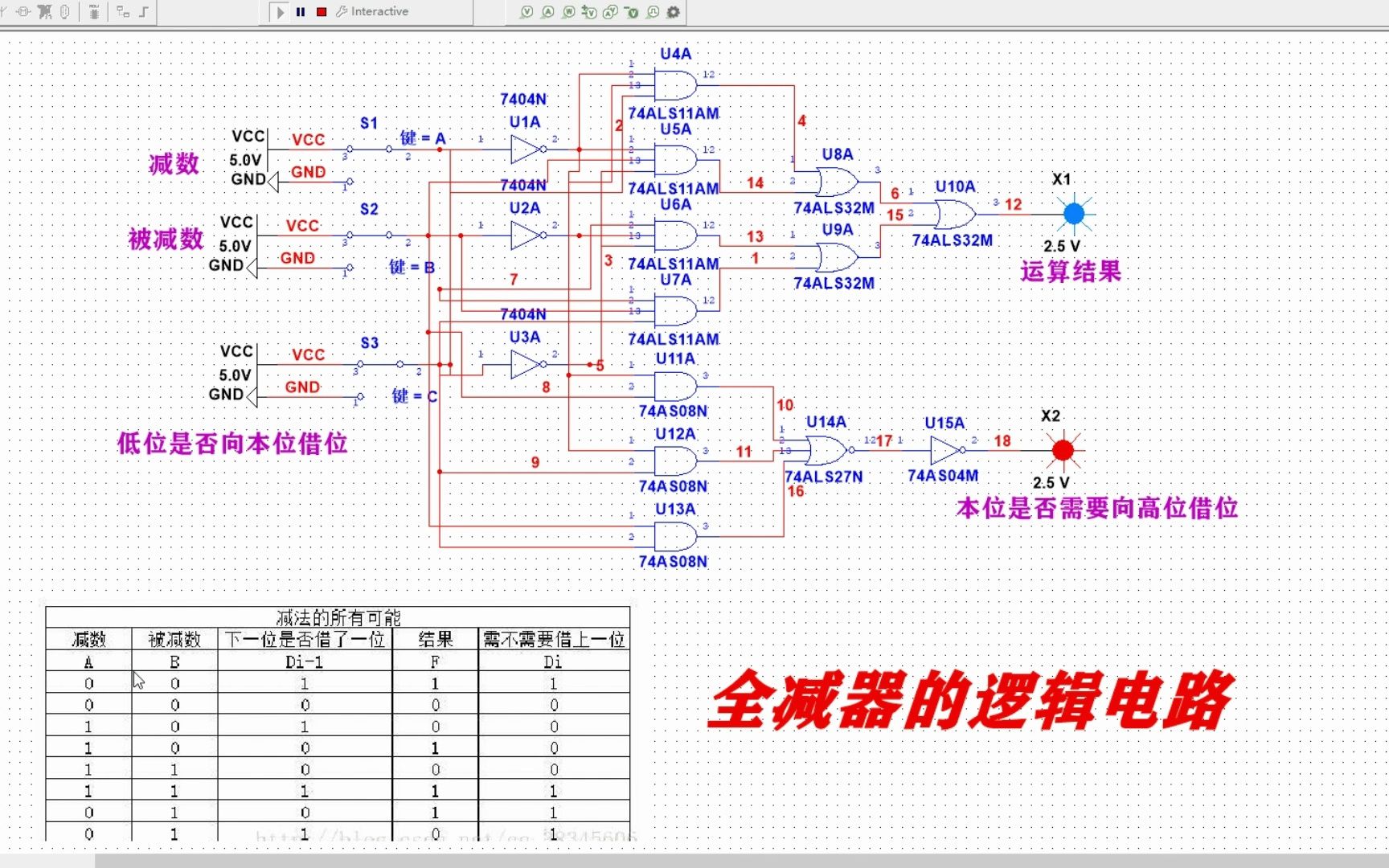

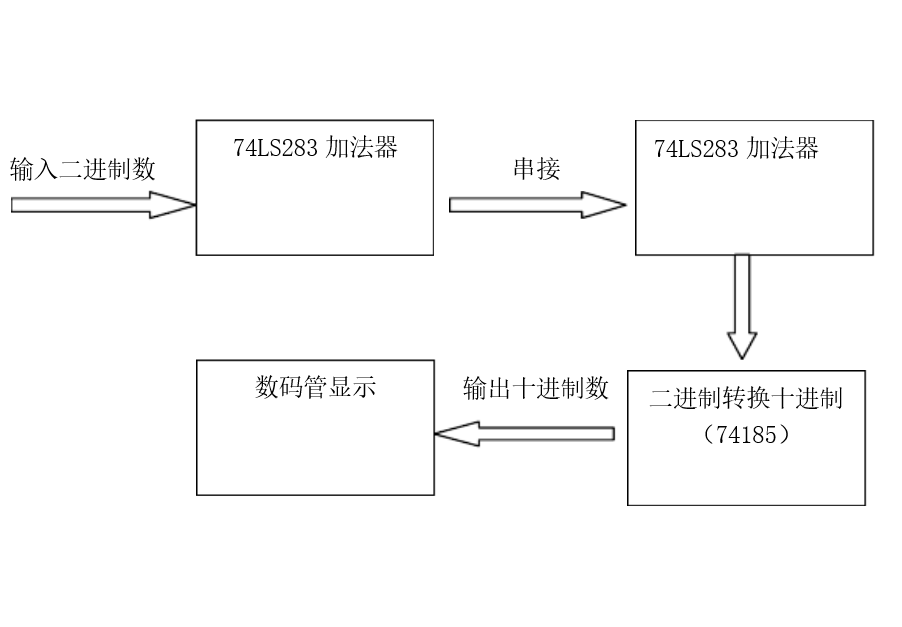

该实验通过全加器串行输入实现8位可控加减法

采用全加器构成的8位二进制补码加减电路

详解74ls138译码器芯片的引脚图及功能工作原理作用全加器全减器等

数字电路 全减器设计(最后结果与非式)

全减器(生活日用品

如图所示电路可实现的逻辑功能是()

8位加法器和减法器设计实习报告

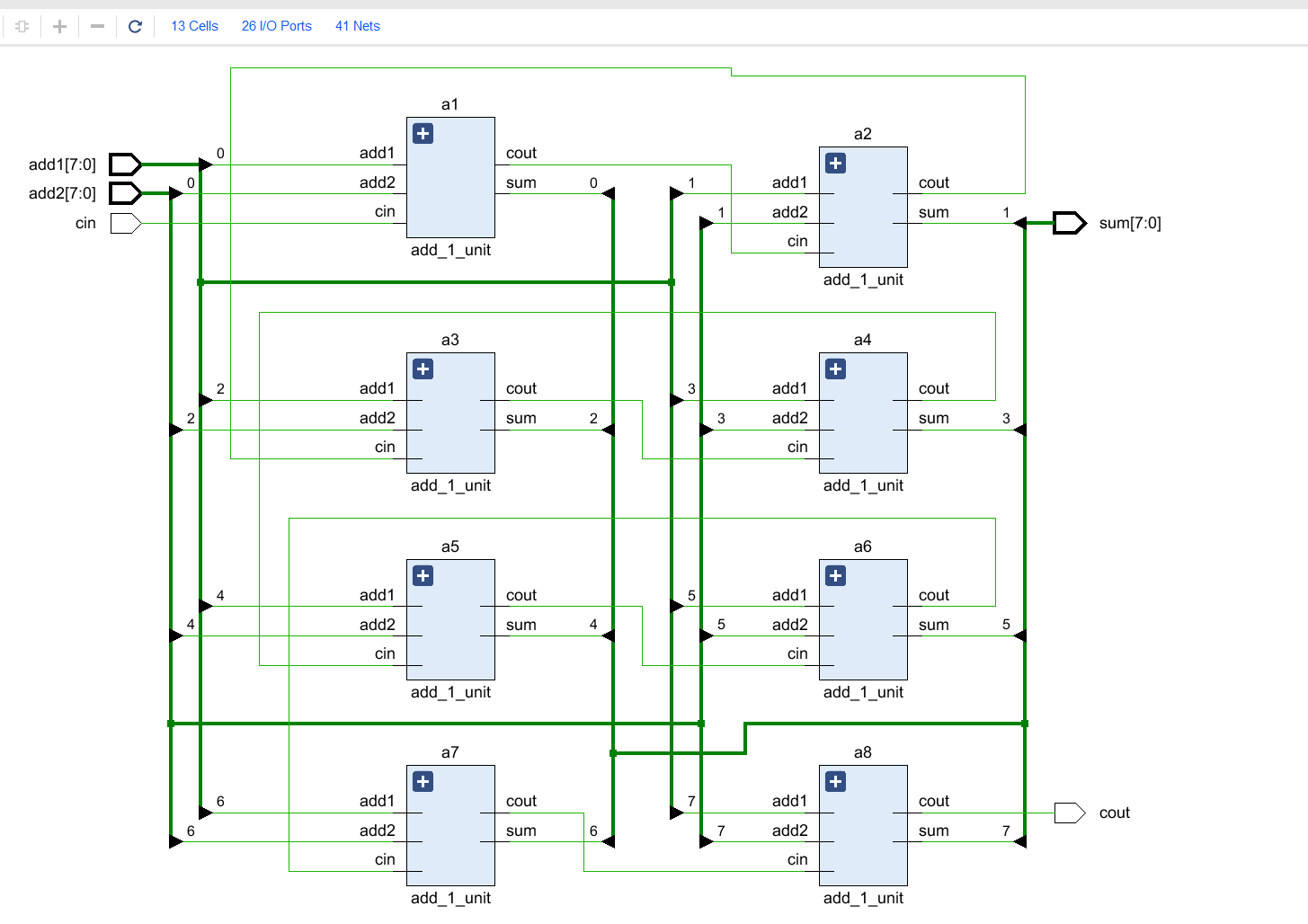

设计8位全加器

用74ls138和与非门实现全减器逻辑电路

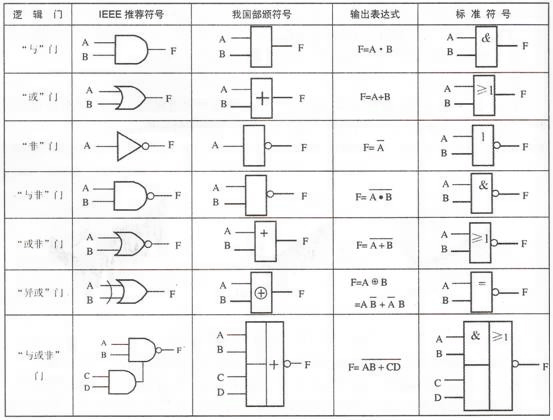

组合逻辑电路的分析方法和种类

[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为

用74ls138和门电路设计1位二进制全减器

全减器的逻辑电路multisim仿真数电设计

设计一个全减器电路

mc14008bcp (motorola [4位全加器]) pdf技术资料下载 mc14008bcp

们分析一位全减器

组合逻辑电路一位全减器设计

减法器

八位加法器

vhdl 八位二进制数减法器

当然减法通过转换成补码也可以用全加器来实现,只不过符号位的处理

全减器

一位全加全减器地实现doc7页

docx免费全文阅读

八位超前进位加法器

更多相关内容:

© 微语生活图库,此页面图片不可商用

微语生活图片下载 使建于2016年,当前更时间:2024-06-01 21:43:53

8位全减器逻辑图图片下载