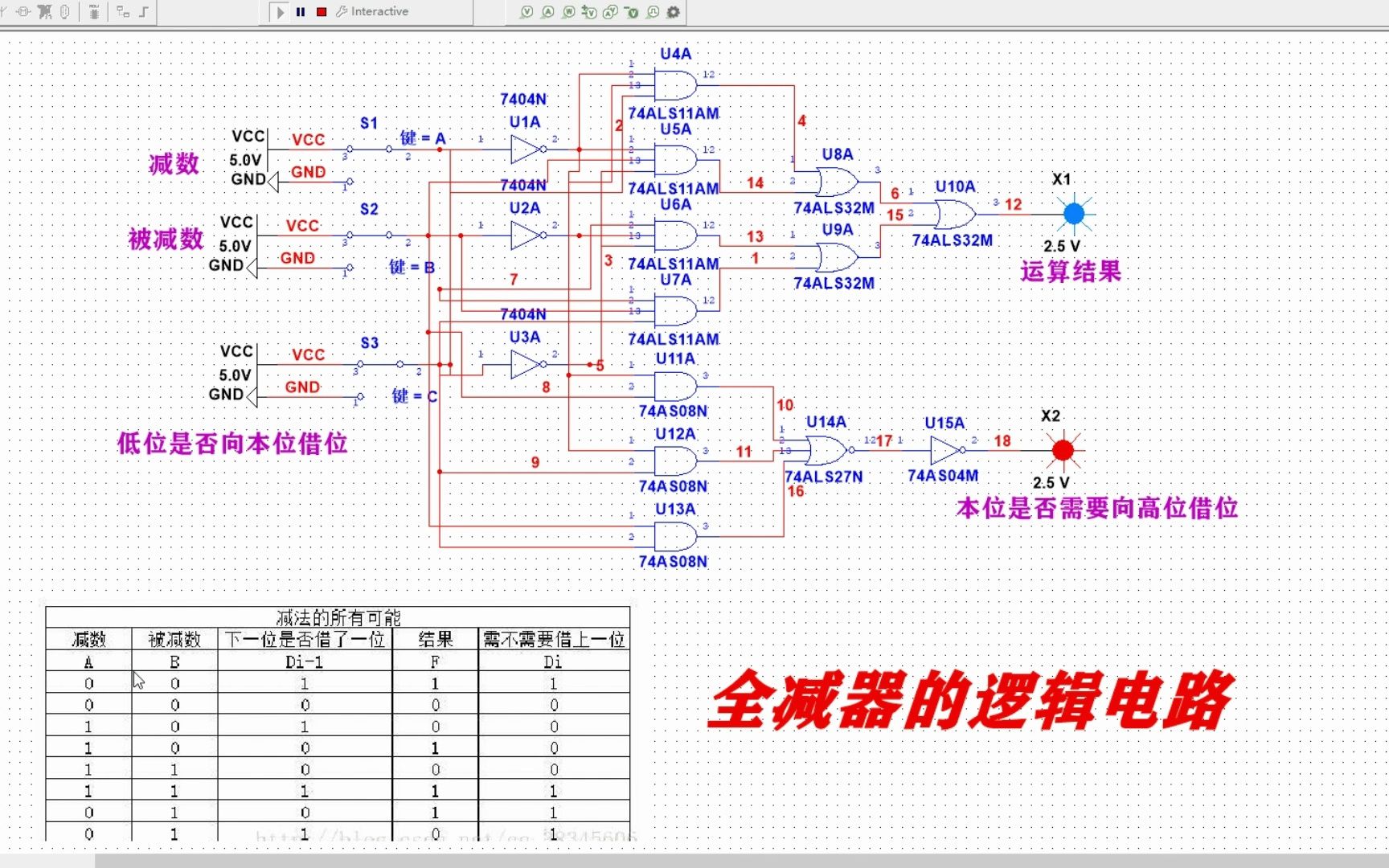

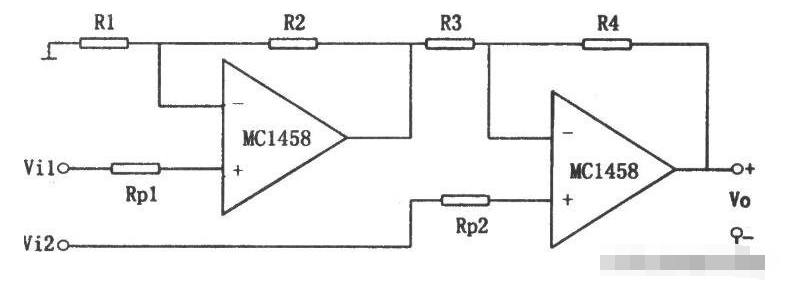

全减器逻辑电路图

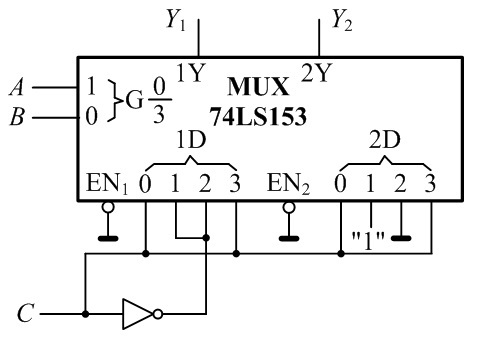

这是38译码器设计的1位二进制全减器,输入为被减数,减数,和来自低位的

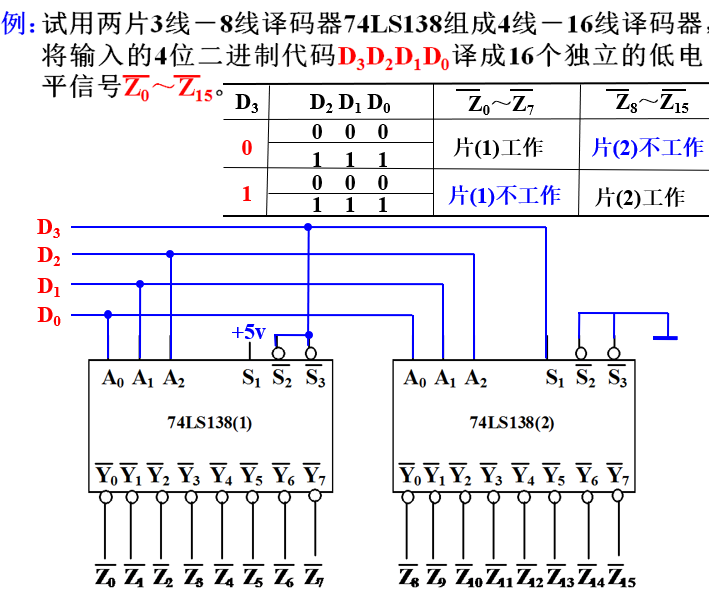

74ls138三线—八线译码器实现,逻辑图如下: 全减器

们分析一位全减器

设计一个全减器电路

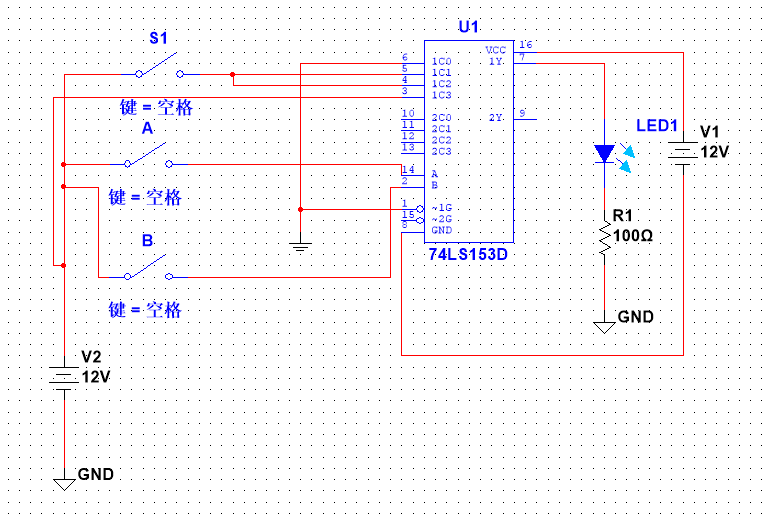

全减器的逻辑电路multisim仿真数电设计

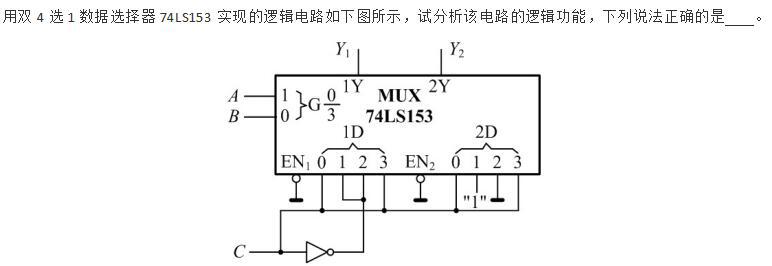

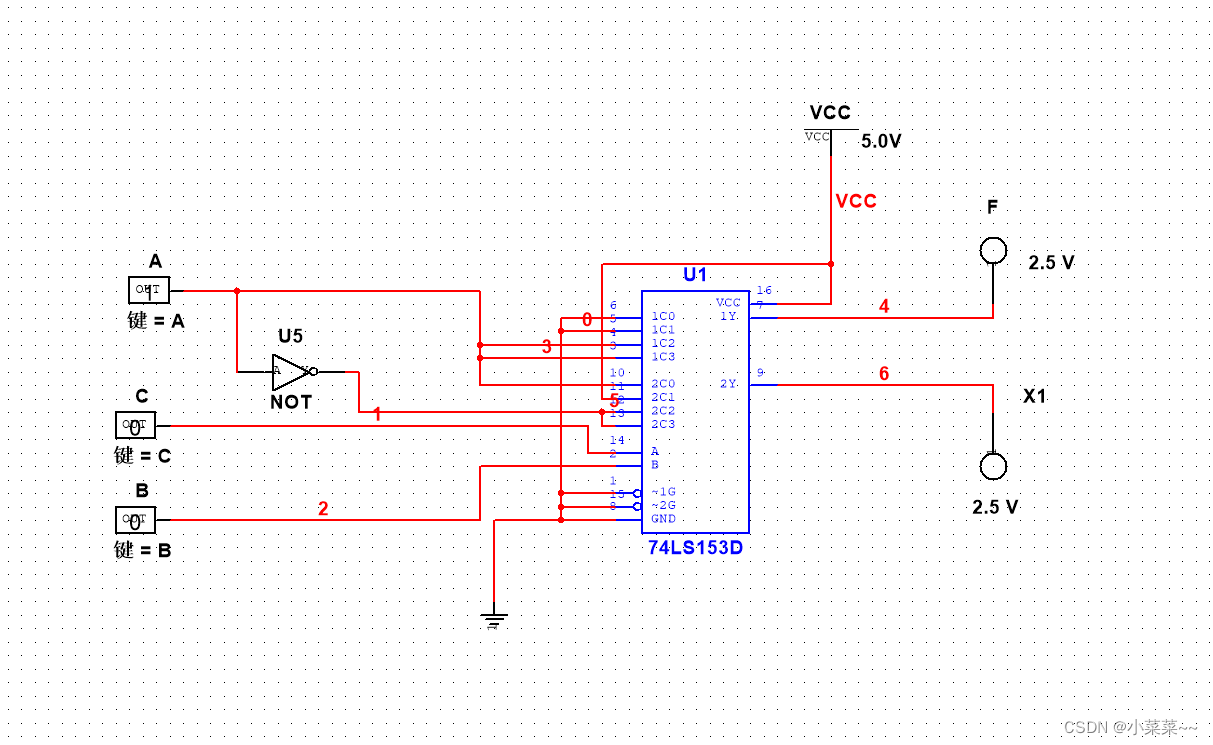

[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为

[图]a,该电路实现全减器的逻辑功能,y1为差的输出,y2为

设计一1位全减器,a为被减数,b为减数,c为来自低位的信号,差为d,向高位

cumt矿大

三款减法器的电路图解析

一位全减器逻辑电路图

三款减法器的电路图解析

应用74ls139译码器和最少的与非门实现全减器

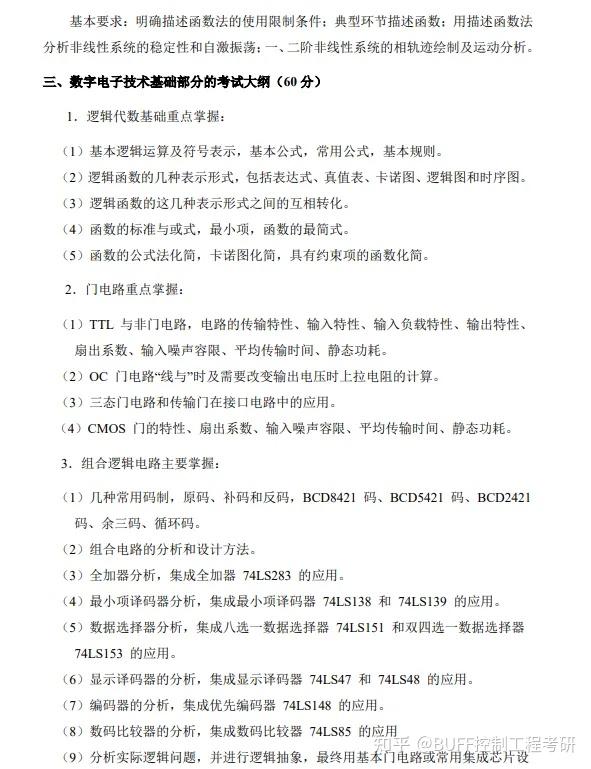

3 编码器74ls148(8线

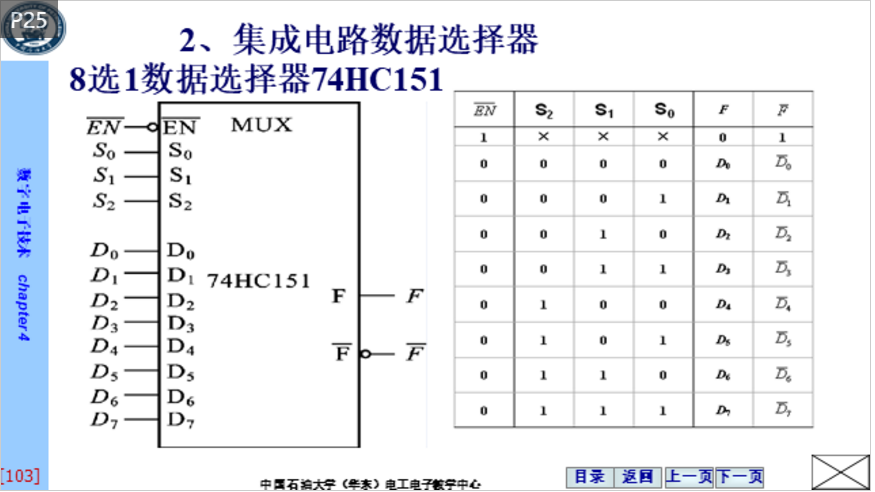

五,用一片4选1数据选择器74153实现逻辑函数 l

电子技术基础74ls153(四选一数据选择器)74ls151(八选一数据选择器)

用vhdl结构描述设计一全减器

真值表和全加器

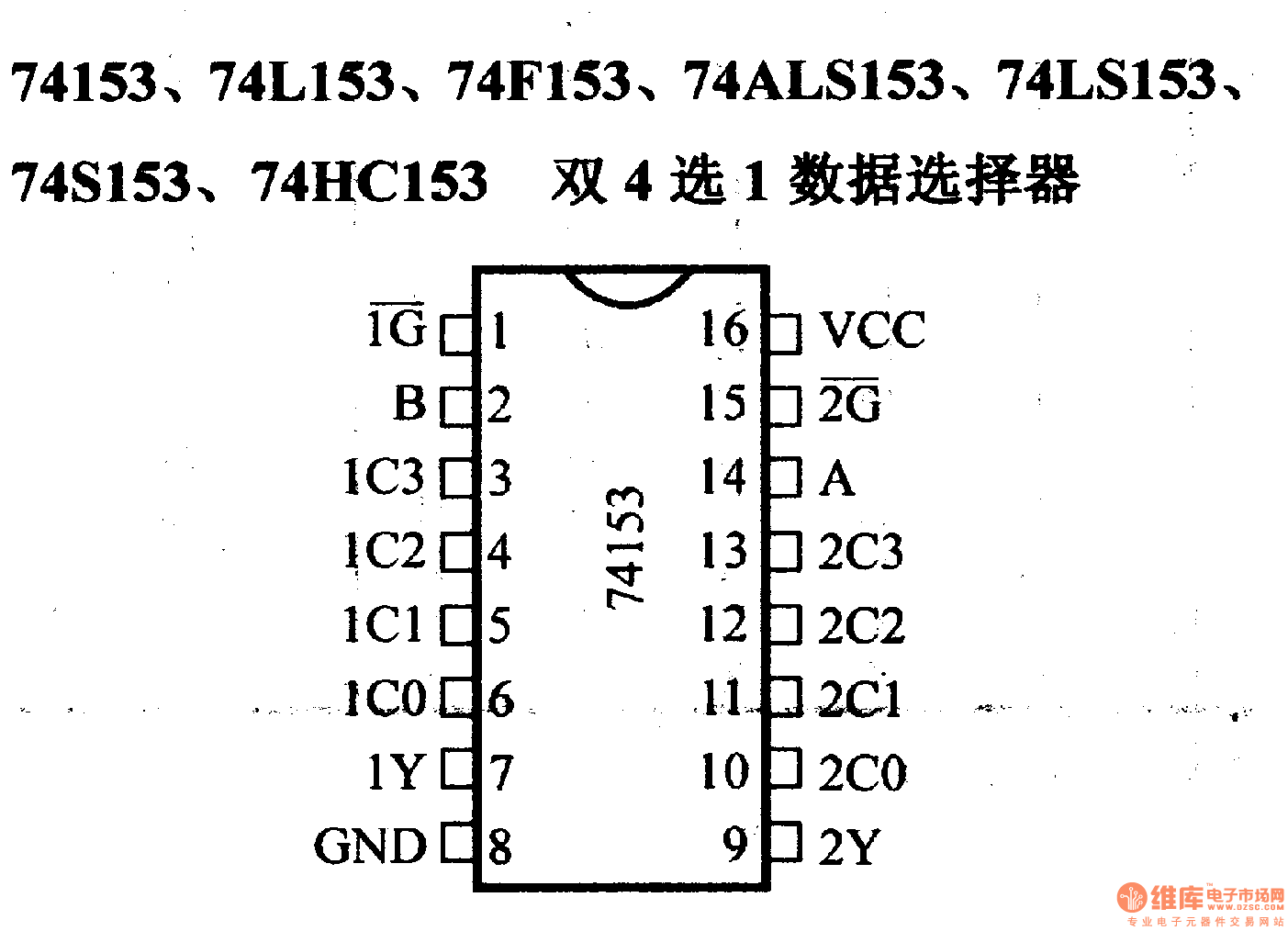

74ls153逻辑符号

2024年北京航空航天大学控制考研录取分析及25考研介绍

原装拍一件=5个 sn74ls153n dip16 双4选1数据选择器芯片 2v~6v

双4选1数据选择器74ls153

用八选一数据选择器74ls151和门电路设计一个电路图74hc151的连接方式

sn74ls153n 双4选1数据选择器 集成电路ic dip16封装

sn74ls145 147 148 151 153 157 160 161 162 163n直插芯片dip

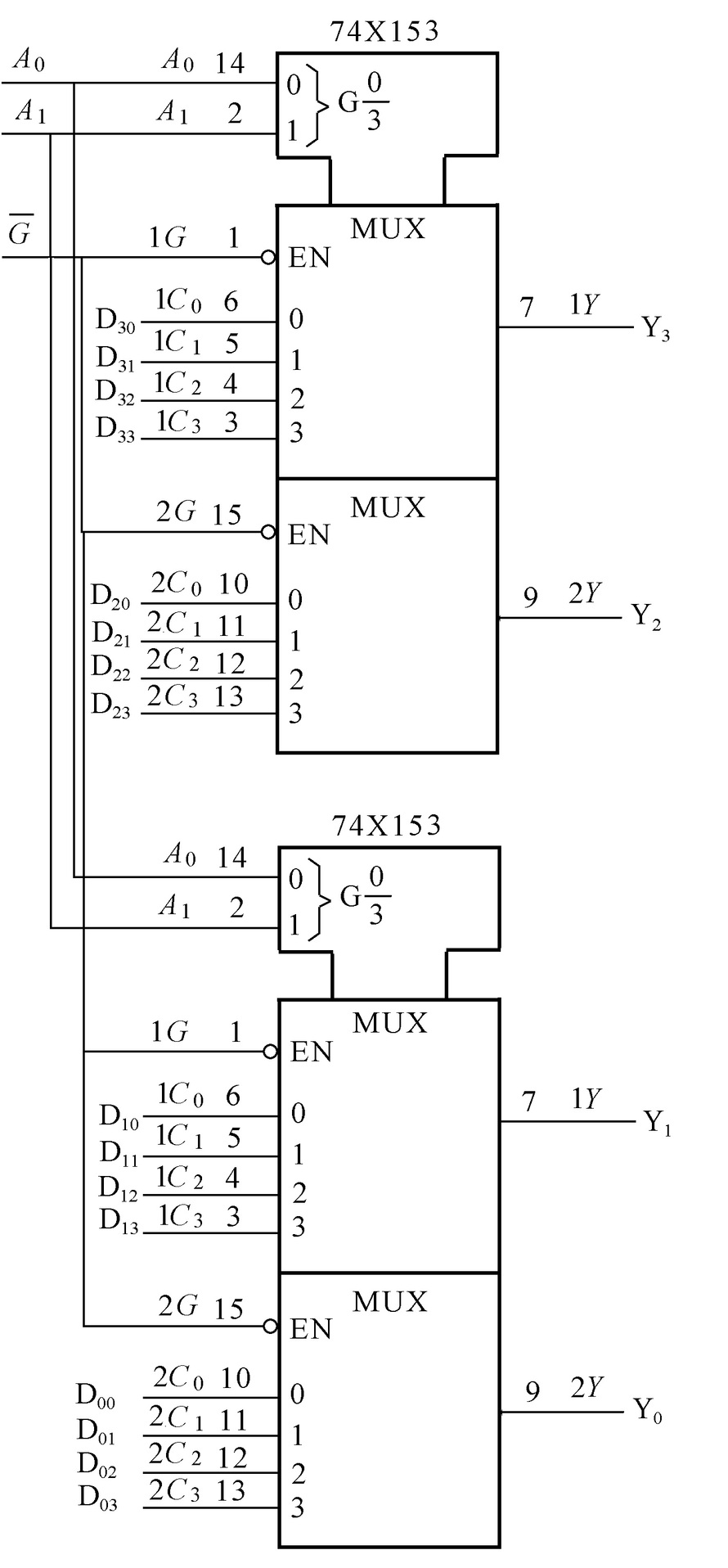

上面是4路四选一数据选择器的功能示意图下面是用两片74x153芯片具体

74系列数字电路74153,74l153等双4选1数据选择器

方案二 使用74ls153数据选择器

用74ls00,74ls153,74ls151,74ls138设计三变量表决器

© 微语生活图库,此页面图片不可商用

微语生活图片下载 使建于2016年,当前更时间:2024-05-31 23:30:52

利用74ls153设计全减器图片下载