当前位置:首页>> 一位全减器74153电路图

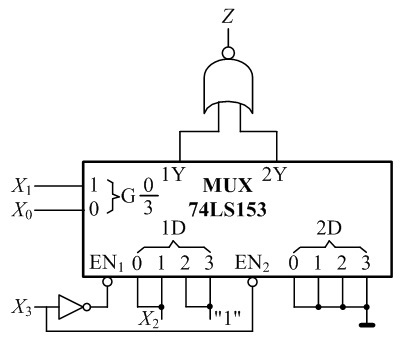

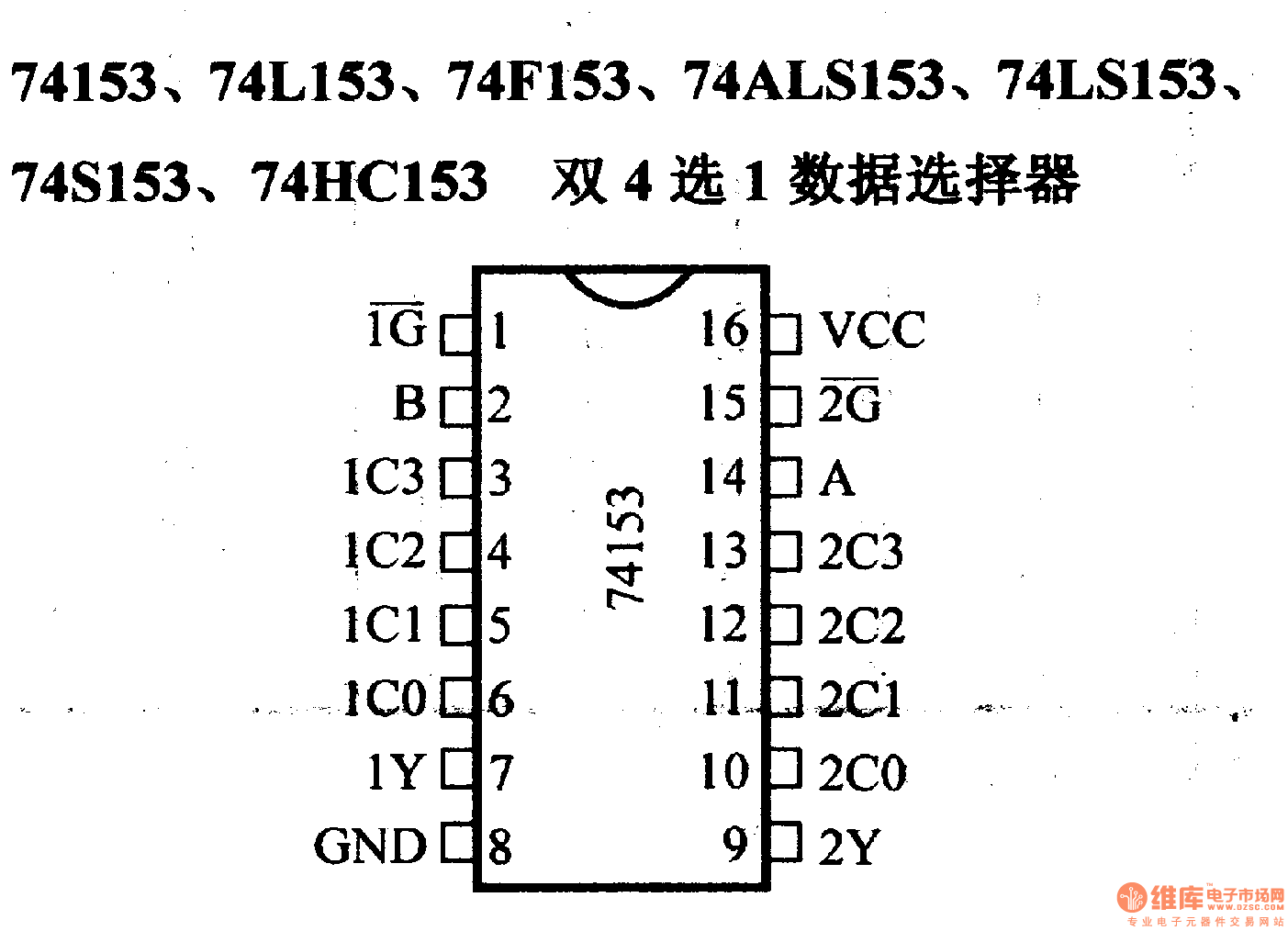

试用双4选1数据选择器74153设计一个全减器它能完成二进制减法运算s

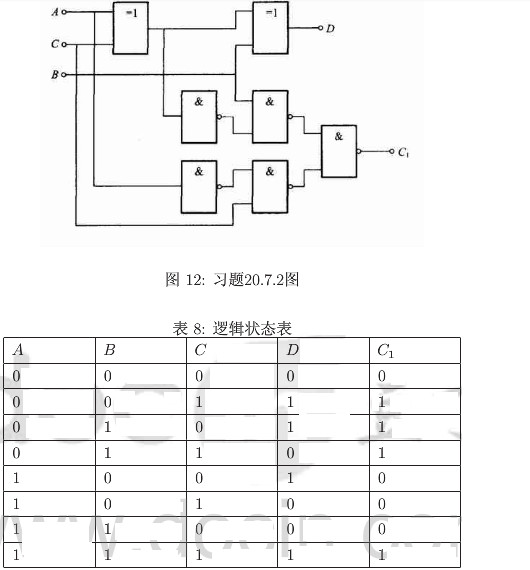

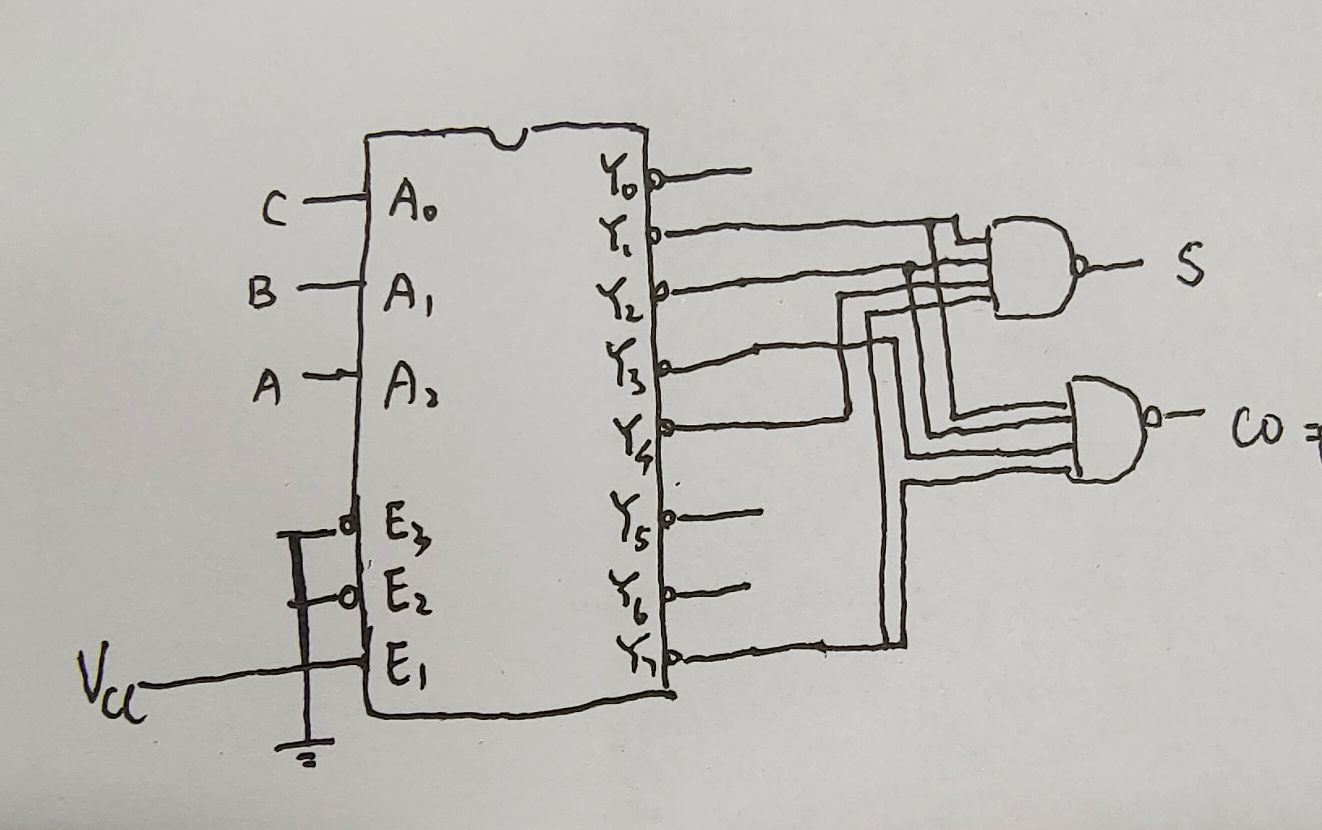

仿照全加器画出1位二进制数的全减器:输入被减数为a,减数为b,低位来的

一位全减器逻辑电路图

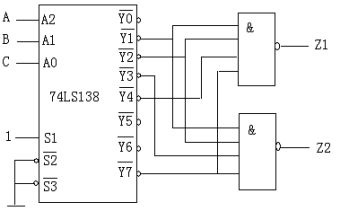

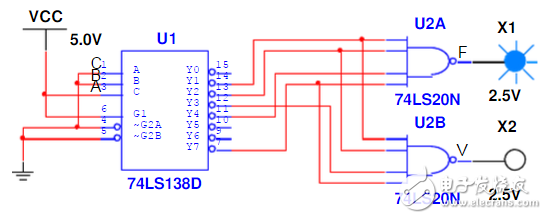

这是38译码器设计的1位二进制全减器,输入为被减数,减数,和来自低位的

全减器逻辑电路图

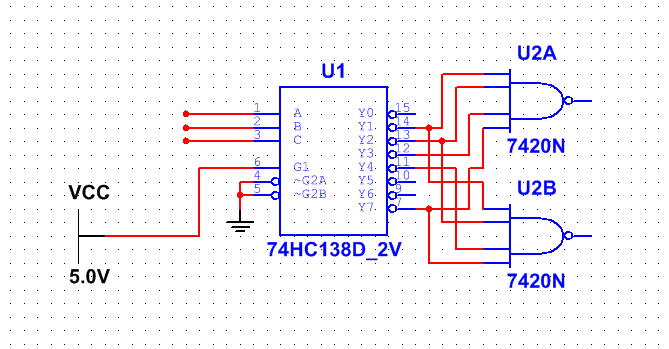

5整体电路图

设计一个全减器电路

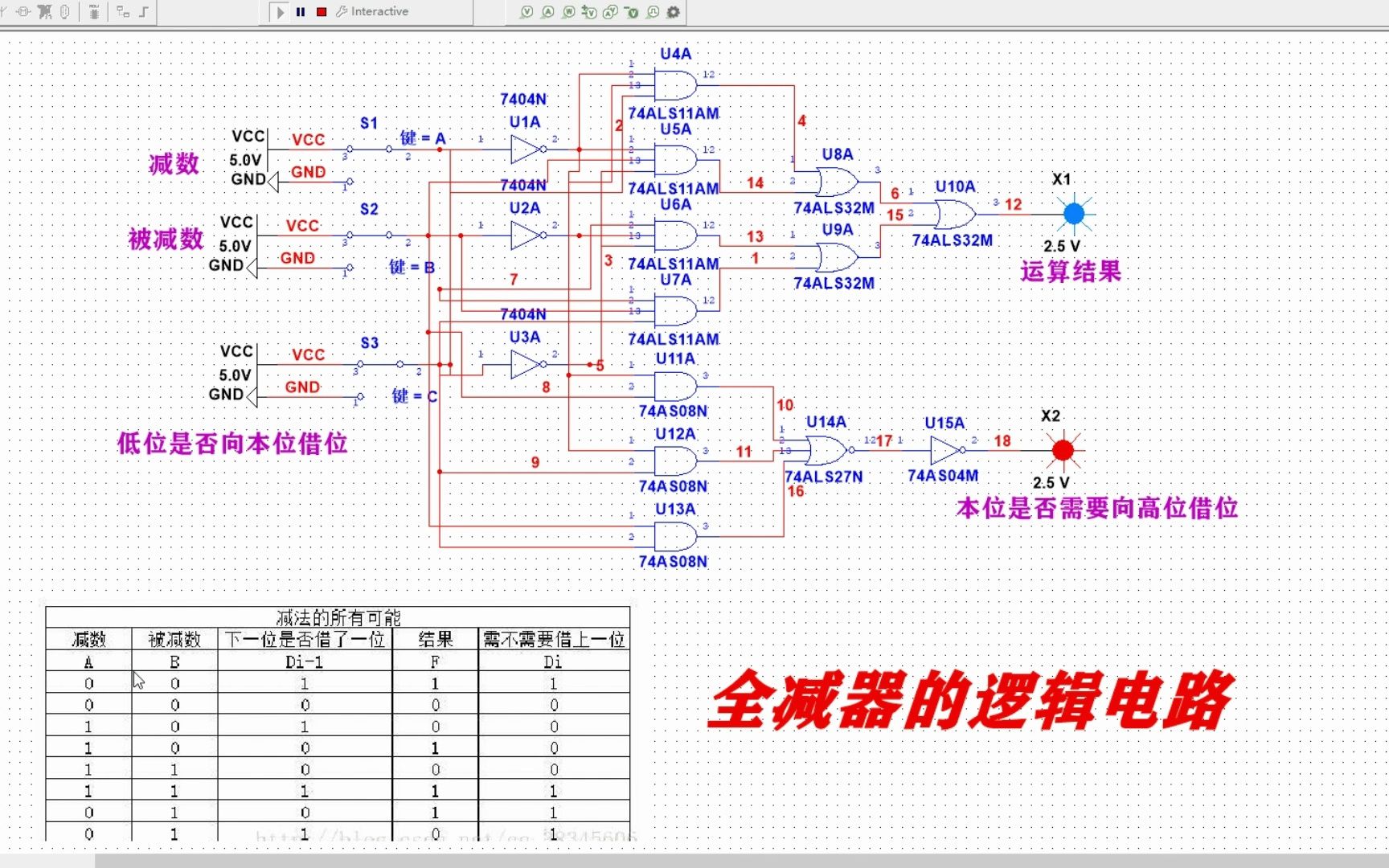

们分析一位全减器

multisim仿真我是新手,但是为什么我下面这个用译码器实现一位全减器

五,用一片4选1数据选择器74153实现逻辑函数 l

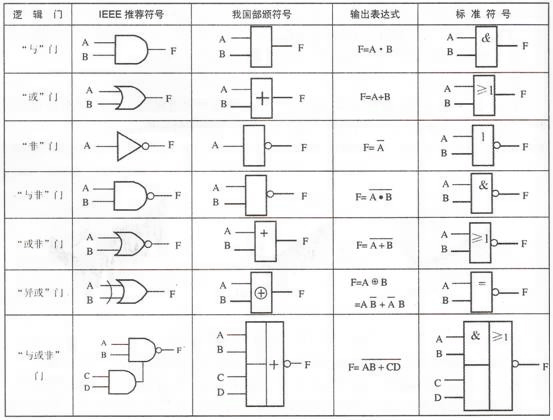

设计一个一位全加减器,采用异或门和与非门来实现该电路 设一控制变量

由双4选1数据选择器74153和门电路组成的组合逻辑电路如下图所示试

组合逻辑电路一位全减器设计

全减器(生活日用品

请问什么叫全减器啊

一位全加全减器地实现doc7页

用vhdl结构描述设计一全减器

设计一1位全减器,a为被减数,b为减数,c为来自低位的信号,差为d,向高位

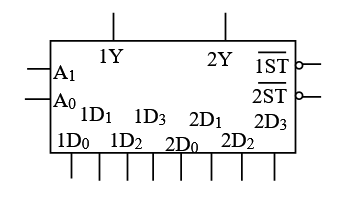

74系列数字电路74153,74l153等双4选1数据选择器

理解全减器的概念,写出一位二进制全减器真值表;3

三款减法器的电路图解析

数字电路 全减器设计(最后结果与非式)

应用74ls139译码器和最少的与非门实现全减器

verilog实现减法器

用74ls138实现一位全减器

全减器

当然减法通过转换成补码也可以用全加器来实现,只不过符号位的处理

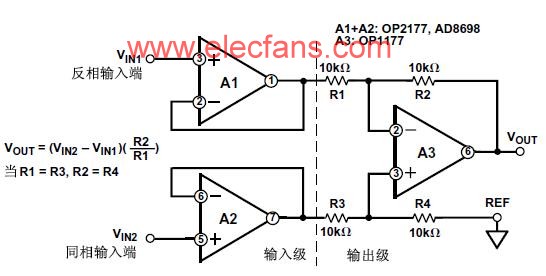

带输入缓冲的减法器电路

用74ls138和门电路设计1位二进制全减器

全减器的逻辑电路multisim仿真数电设计

最近更新的...

更多相关内容:

© 微语生活图库,此页面图片不可商用

微语生活图片下载 使建于2016年,当前更时间:2024-06-08 07:53:52

一位全减器74153电路图图片下载